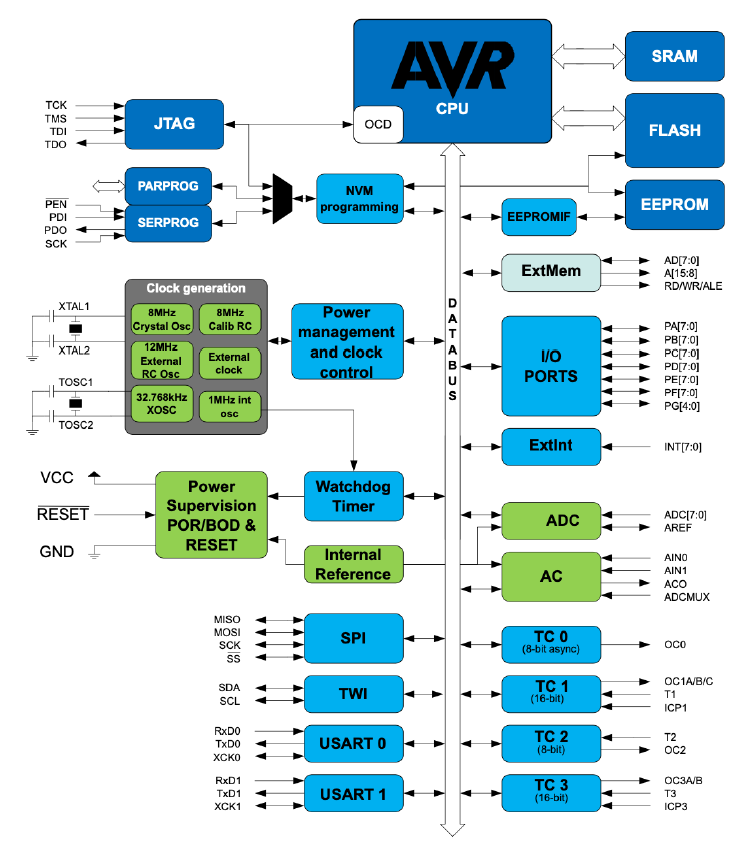

ATmega 128 구조개요 지난 시간에 ATmega 128에 대한 대략적인 개요를 파악했었다. 이번 시간에는 ATmega 128의 CPU와 메모리 구조를 파악해 보는 시간을 가지도록 해보자. 시작하기 앞서 ATmega 128은 프로그램(SRAM)과 데이터(FLASH, EEPROM)가 분리되어 있으므로 Harvard 구조를 채택하고 있다는 점 알아두자. 그리고, 해당 구성요소들은 컴퓨터 구조 시간에서 한 번씩 다뤘던 내용이므로, 헷갈린다면 해당 게시글들을 확인해 보자.본문CPU 구조 ATmega 128의 CPU 구조다. 여기서 ALU를 포함해 범용 레지스터(General Purpose Register), 상태 제어 레지스터(Status and Control), 프로그램 카운터, 플래시 메모리, 명령 ..