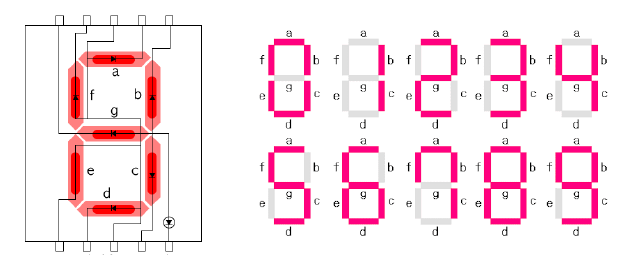

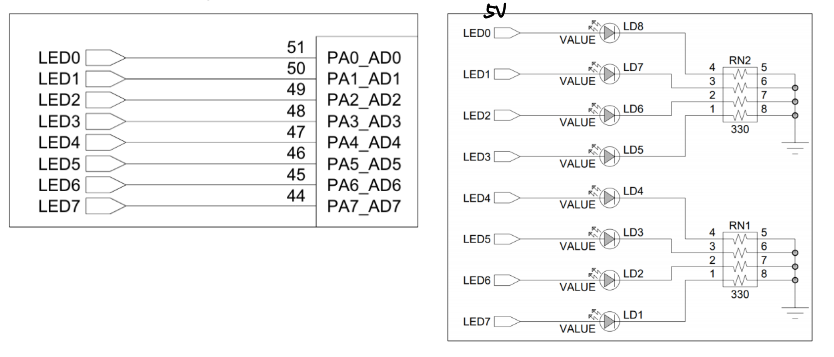

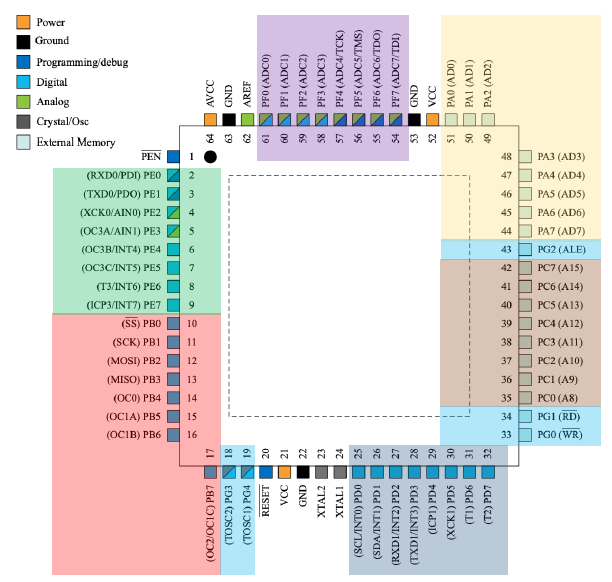

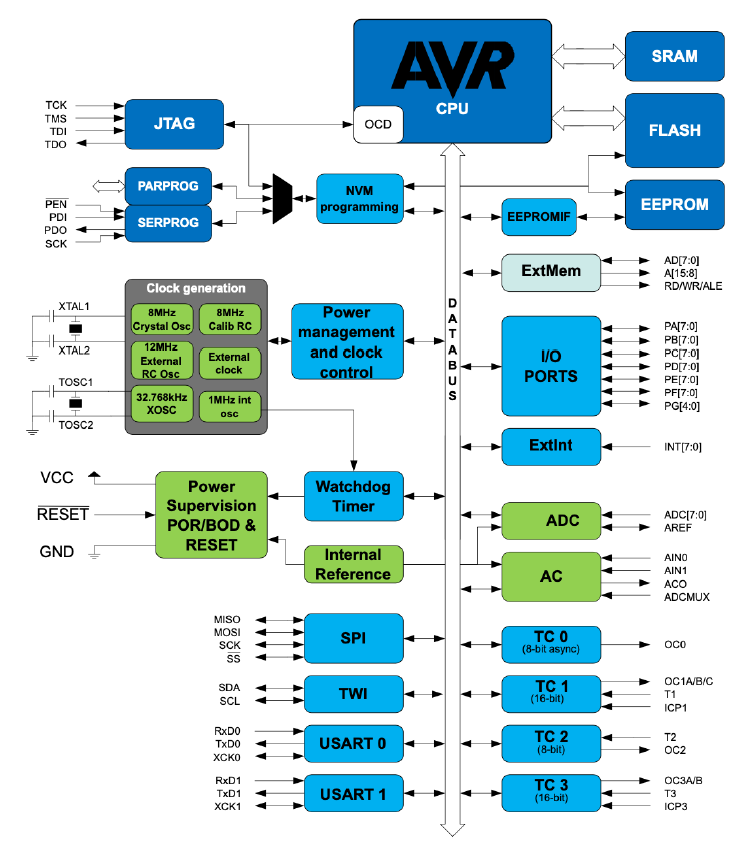

본문 FND 제어 이번 시간에는 FND(Flexible Numeric Display)를 조작해 보는 시간을 가지도록 해 보자. 7-segments로도 알려진 FND는 LED의 어느 단자를 공통 단자로 사용하느냐에 따라 Common Anode와 Common Cathode로 나뉜다. Common Anode는 모든 LED의 Anode가 공통으로 연결되어 있어, LED를 점등시키려면 해당 LED의 Cathode에 GND를 공급해야 한다. 반면 Common Cathode는 모든 LED의 Cathode의 Cathode가 공통으로 연결되어 있어, LED를 점등시키려면 해당 LED의 Anode에 전압을 공급해야 한다. J-KIT-128-1의 경우 공동 음극형으로 설계되어 있다. FND의 구동 방식은 모든 LED 제어 ..