USART 통신 개요

개요

데이터를 모니터에 출력하려면, 메인보드와 HDMI를 연결하여 데이터를 송/수신해야 한다. 이처럼 장치 간 데이터를 주고받을 때, 하나의 신호선을 직렬로 연결하여 사용하는 통신 방식을 USART(Universal Synchronous and Asynchronous Receiver and Transmitter)라고 한다. 이번 시간에는 비동기 방식을 다루도록 해보겠다.

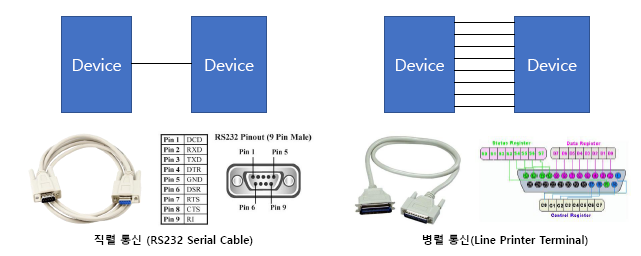

- 직렬 통신(Serial Communication): 순차적으로 데이터를 한 번에 하나의 비트만 송수신하는 통신 방법

- 병렬 통신(Parallel Communication): 여러 개의 채널을 통해 여러 비트를 송수신하는 통신 방법

- 동기식(Synchronous) 통신: 기준 클럭에 맞춰 데이터를 송수신하는 방법

- 비동기식(Asynchronous) 통신: 전송 속도를 정하고 각자 클럭을 사용하여 데이터를 송수신하는 방법

이때 동기/비동기가 필요한 이유는 디지털 신호를 사용하지만 연속적으로 데이터를 주고받으므로 속도를 맞춰야 정보를 구분할 수 있기 때문이다. 예를 들어 위와 같이 01010101이라는 데이터가 송신되었을 때, 수신하는 측에서 클럭에 따라 데이터가 달라진다. 위와 같이 서로 다른 디바이스가 데이터를 주고받기 위한 통신 규약을 프로토콜(Protocol)이라고 한다.

본문

ATmega128의 USART

ATmega128에서 USART는 전이중 방식의 통신 모드를 지원한다. 또한 비동기/동기식의 통신 모드를 모두 지원하며 분해능이 좋은 Baud Rate 발진기를 내장하고 있다. 그리고, 다양한 직렬 통신 프레임을 지원하며 오류 정정을 위한 패리티 발생 및 검사 기능을 하드웨어적으로 지원한다.

- 전이중 방식(Full-duplex): 송신과 수신이 동시에 가능

- 반이중 방식(Half-duplex): 송신과 수신 동시에 불가

또한 ATmega128에서는 비동기식 직렬 통신을 위한 통신 인터페이스 RS-232C를 사용한다. 물리적 연결 방식으론 우측의 사진과 같이 DB-9와 같은 형태를 사용하고, 프레임 포맷(Frame Foramte)은 시작 비트, 데이터 비트, 패리티 비트, 정지 비트를 사용한다.

USART 제어(1) - UDRn 레지스터

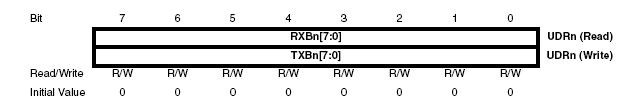

먼저 송수신 데이터 버퍼 기능을 수행하는 UDRn(USART I/O Data) 레지스터다. 이때 송신 버퍼 레지스터와 수신 버퍼 레지스터는 물리적으로 별개이나, 동일한 I/O 주소를 사용한다. 이는 하나의 레지스터 주소를 사용하여 데이터를 송수신할 수 있으므로 자원을 절약할 수 있다는 장점이 있다. 송신할 데이터를 UDRn 레지스터에 쓰면 TXBn 레지스터에 저장되고, 수신할 데이터를 UDRn 레지스터로부터 읽으면 RXBn 레지스터에 내용이 읽힌다.

USART 제어(2) - USRnA 레지스터

USART의 제어와 상태를 담당하는 레지스터들은 A, B, C 3개로 나뉘어 있다. 이때 각 기능을 구현하기 위해 다른 레지스터와 연계해서 사용되는 부분도 존재한다.

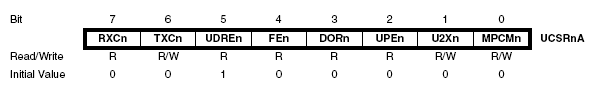

먼저 오류를 검출하거나, 준비 완료 상태를 발생시키는 UCSRnA 레지스터다.

1. RXCn: 데이터 수신이 완료되어 버퍼에 문자가 있으면 1로 설정되고, 없으면 0으로 클리어되는 비트다. 만약 폴링 방식을 사용한다면 수신 데이터를 읽으면 0으로 클리어된다. 이때 USCRnB 레지스터의 RXCIEn 비트가 1로 설정되어 있을 경우 수신 완료 인터럽트를 발생시키며, ISR 실행 시 자동으로 클리어된다.

2. TXCn: 폴링 방식을 사용할 경우 데이터 송신이 완료되어 버퍼에 문자가 없으면 1로 설정되고, 있으면 0으로 클리어된다. 만약 USCRnB 레지스터의 TXCIEn 비트가 1로 설정되어 있을 경우 송신 완료 인터럽트를 발생시키고, ISR 실행 시 자동으로 0으로 클리어된다.

3. UDREn: 데이터 송신 버퍼가 비어 새로운 데이터를 쓸 준비가 되어 있으면 1로 설정되는 비트다. 송신 버퍼는 UCSRnA 레지스터의 UDREn 플래그가 1로 설정된 경우에만 쓰기가 가능하다. 만약 USCRnB 레지스터의 UDRIEn 비트가 1로 설정되어 있을 경우, 데이터 레지스터 준비 완료 인터럽트를 발생시킨다. 또한 MCU가 리셋된 후에는 송신기의 준비 상태를 나타내기 위해 1로 초기화되며, ISR 실행 시 자동으로 클리어된다.

4. FEn: UDRn의 수신 버퍼에 수신된 데이터를 읽는 동안 프레임 오류 감지 시 1로 설정되는 비트다. 해당 오류는 수신한 문자의 첫 번째 정지 비트가 0으로 읽히면 발생하고, 수신 버퍼 UDRn을 읽을 때까지 유효하다. 만약 UCSRnA 레지스터에 쓰기를 실행하면 0으로 클리어된다.

5. DORn: 데이터를 수신 시 오버런 오류가 감지되면 1로 설정되는 비트다. 해당 오류는 수신 버퍼에 현재 읽지 않은 문자가 있는 상태에서 다른 문자의 시작 비트를 수신하면 발생한다. 이 플래그는 수신 버퍼 UDRn을 읽을 때까지 유효하고, UCSRnA 레지스터에 쓰기를 실행하면 0으로 클리어된다.

6. UPEn: 데이터를 수신 시 패리티 오류가 감지되면 1로 설정되는 비트다. 해당 오류는 UCSRnC 레지스터의 UPMn1 비트를 1로 설정하여 패리티를 검사하도록 설정한 경우에만 발생하며, UDRn을 읽을 때까지 유효하다. 또한 UCSRnA 레지스터에 쓰기를 실행하면 0으로 클리어된다.

7. U2Xn: USART의 클럭 분주비를 16에서 8로 낮추어 전송 속도를 2배로 설정하는 모드다. 이는 비동기 모드에서만 유효하다.

8. MPCMn: 1개의 마스터가 여러 개의 슬레이브와 통신하는 다중 프로세서 통신 모드를 설정하는 비트다.

USART 제어(3) - USRnB 레지스터

인터럽트, 사용 허가, 문자 길이 설정 등을 담당하는 UCSRnB 레지스터다.

1. RXCIEn: 수신 완료 인터럽트를 개별적으로 허가하는 비트다. 이 비트가 1로 설정되어 있고, SREG.I가 1로 설정되어 있으면 UCSRnA 레지스터의 RXCn 비트가 세트될 때 수신 완료 인터럽트를 발생시킨다.

2. TXCIEn: 송신 완료 인터럽트를 개별적으로 허가하는 비트다. 이 비트가 1로 설정되어 있고, SREG.I가 1로 설정되어 있으면 UCSRnA 레지스터의 TXCn 비트가 세트될 때 수신 완료 인터럽트를 발생시킨다.

3. UDRIEn: 데이터 레지스터 준비 완료 인터럽트를 개별적으로 허가하는 비트다. 이 비트가 1로 설정되어 있고, SREG.I가 1로 설정되어 있으면 UCSRnA 레지스터의 UDREn 비트가 세트될 때 수신 완료 인터럽트를 발생시킨다.

4. RXENn: USART의 수신부 사용을 허가하는 비트다. 이 비트를 0으로 설정하면 범용 I/O 단자로, 1로 설정하면 직렬 통신 데이터 수신 단자로 동작하며 이때에만 FE(Frame Error), DOR(Data OverRun), UPE(USART Parity Error)의 동작이 유효하다.

5. TXENn: USART의 송신부 사용을 허가하는 비트다. 이 비티를 0으로 설정하면 범용 I/O 단자로, 1로 설정하면 직렬 통신 데이터 송신 단자로 동작한다. 이 비트를 0으로 설정하면 현재 송신 중인 데이터의 송신이 완료될 때까지 유효하지 않는다. 즉, 중간에 통신이 끊기지 않는다.

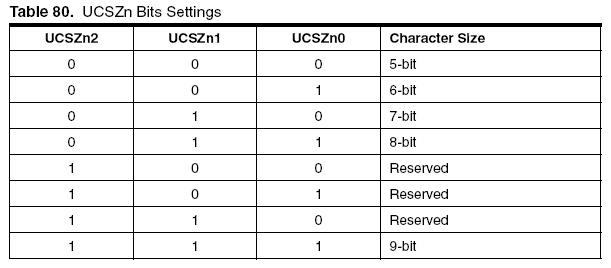

6. UCSZn2: 한 프레임 내 전송 문자 길이를 설정하는 비트다. UCSRnC 레지스터의 USCZn1:0 비트와 함께 설정해야 한다.

7. RXB8n: 전송 문자의 길이가 9비트로 설정된 경우, 수신된 문자의 9번째 비트를 저장한다. 반드시 UDR 레지스터보다 먼저 읽어야 하는데, 이는 9번째 비트의 정보가 새로운 수신에 의해 덮어 쓰일 위험이 있기 때문이다. 즉, 하위 비트부터 쓰는 ATmega128 AVR의 특성 때문에 이러한 순서가 결정된다.

8. TXB8n: 전송 문자의 길이가 9비트로 설정된 경우, 송신할 문자의 9번째 비트를 저장한다. 이 또한 UDR 레지스터보다 먼저 써야 한다.

USART 제어(4) - USRnC 레지스터

정지 비트 수, 전송 문자의 길이, 송수신 시점 등을 결정하는 UCSRnC 레지스터다.

1. UMSELn: USART의 동작 모드를 설정하는 비트다. 비동기식 모드는 0, 동기식 모드는 1로 쓴다.

2. UPMn1/UPMn0: 패리티 모드를 설정하는 비트다. 패리티 없음, 짝수 패리티, 홀수 패리티 중 하나를 선택할 수 있다.

3. USBSn: 데이터 프레임의 정지 비트 수를 설정하는 비트다. 이 비트를 1로 설정하면 정지 비트를 2로, 0으로 설정하면 1비트로 설정한다.

4. UCSZn1-0: UCSRnB 레지스터의 UCSZn2 비트와 함께 전송 문자의 길이를 설정하는 비트다.

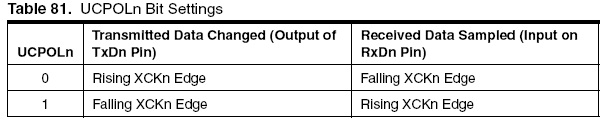

5. UCPOLn: 동기 모드 사용 시 동기 클럭에 대한 송수신 시점을 결정하는 비트다. 비동기 모드에서는 0으로 설정하여 사용하지 않는다.

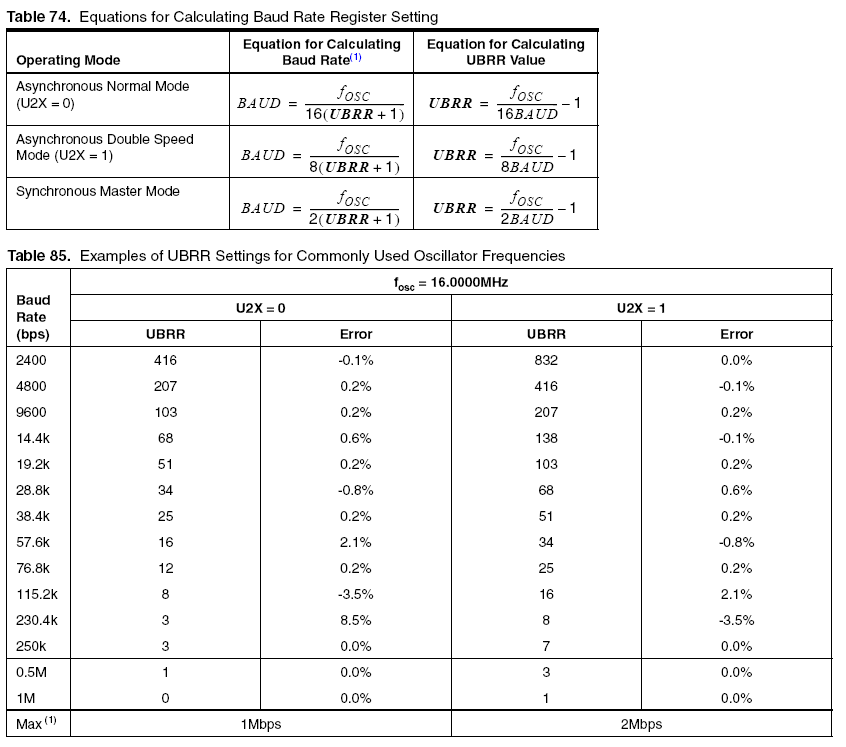

USART 제어(5) - UBRRnL/H

USARTn 포트의 송수신 속도를 결정하는 UBRRnL/H 레지스터다. 즉, 포트의 송수신 속도를 결정하는 비트로써 Baud Rate(bps)와 UBRR 값을 이용해 결정한다.

- Baud Rate: 직렬 통신에서 데이터가 전송되는 속도(단위: Baud)

다음은 자주 사용되는 Baud Rate와 이를 위한 UBRR 레지스터 값이다.

요약

ATmega128의 USART 통신

1. 정의: 하나의 신호선을 직렬로 연결하여 사용하는 통신 방식

2. 특징

a. 전이중 방식 통신 모드

b. 비동기/동기식 모드 지원

3. 레지스터

a. UDRn: 송수신 데이터 버퍼

b. UCSRnA

① UCSRnB와 연계하여 수신/송신 완료, 수신 준비 완료를 설정

② 프레임, 오버런, 패리티 오류 감지

③ 전송 속도 조절, 다중 프로세서 통신 모드 설정

c. UCSRnB

① UCSRnA와 연계하여 수신/송신 수신 준비 완료, 수신/송신부 사용 허가

② UCSRnC와 연계하여 한 프레임 내 전송 문자 길이 설정

③ 전송 문자 길이가 9비트인 경우 송/수신 문자의 9번째 비트를 저장

d. UCSRnC

① 동기/비동기식 모드, 패리티 모드 설정

② 데이터 프레임의 정지 비트수 설정 및 송수신 시점 결정

③ UCSRnB 레지스터와 연계하여 한 프레임 내 전송 문자 길이 설정

e. UBRRnL/H: 송수신 속도 Baud Rate를 결정하는 레지스터

'CS > 마이크로프로세서' 카테고리의 다른 글

| [마이크로프로세서] ADC(Analog-Digital Converter) (2) | 2024.01.15 |

|---|---|

| [마이크로프로세서] 타이머/카운터 정리 (1) | 2024.01.10 |

| [마이크로프로세서] 타이머/카운터 및 예제(2) (2) | 2024.01.03 |

| [마이크로프로세서] 타이머/카운터 및 예제 (1) (2) | 2023.11.28 |

| [마이크로프로세서] 타이머/카운터 (3) (2) | 2023.11.27 |